本研究グループでは,ユビキタス社会や省エネルギー社会(グリーン社会)の実現を支える情報処理デバイスの研究を行っています。次のようなことに興味がある方,大歓迎です。

・ 新しいナノエレクトロニクス材料

〜 ナノワイヤ、グラフェン、シリセン、ゲルマネン

・ 最先端CMOSトランジスタ

・ 新しい原理/概念を導入したグリーンナノデバイス

・ 原子層科学(2次元材料/デバイス)

・ コンピュータシミュレーション

他の研究機関とのプロジェクト研究に興味がある人は,プロジェクトに参加することも可能です。優れた研究成果を出した学生には,積極的に学会発表することを勧めています。学生の国際会議での発表も多数行われています。学生の学会発表活動については,こちらをご覧下さい。

本研究グループでは,「従来の枠組みや発想にとらわれず,新しい世界を切り拓く」をモットーにしています。

参考)卒研テーマ説明会プレゼン資料

研究内容

本格的なIT化に伴い、社会で扱う情報量は2025年には2006年比で約200倍になると見込まれています(経済産業省の試算より)。これに伴って情報を処理するIT機器の台数が増加するとともに、各機器の情報処理量が増大するためIT機器全体による消費電力量が急増すると見込まれています。したがって、情報社会の継続的な発展を維持するためには、IT機器の消費電力を桁違いに低減させることができる画期的な技術の開発が求められています。その研究を行う分野をグリーンナノエレクトロニクスとよびます。

本研究グループでは、グリーンナノエレクトロニクスを実現するためのキーテクノロジーとして、これまでLSIの進歩を支えてきた微細化技術に代わり、新しい発想に基づくナノデバイスの開発が不可欠であると考えています。将来の省エネルギー・ユビキタス社会を支える情報処理デバイス(トランジスタ)のあるべき姿を探るため、以下の視点を中心に研究を行っています。

●シリコンでどこまで行けるか (More Moore)

●新材料・新構造で性能/機能を向上させる (More than Moore)

●新しい原理で動かす (Beyond CMOS)

●Beyond the Technology Road Map

研究活動の例をいくつか紹介します。

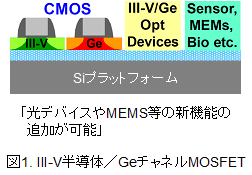

■新材料・新構造CMOSデバイス

Siよりも優れた特性を持つIII-V族化合物半導体[1]やグラフェン[2-4]をトランジスタに応用する研究を行っています。III-V族化合物半導体は、半導体レーザやHEMT等に用いられる高性能半導体材料です。一方、グラフェンは炭素で作られる原子1層の薄膜で、Siに比べて数千倍 ~ 一万倍の非常に高い電子移動度を示すことが知られています。そのため、III-Vチャネルトランジスタやグラフェンチャネルトランジスタが実現できれば、LSIの消費電力を1ケタ以上低減できると期待されています。ただしグラフェンはバンドギャップを持たないため、そのままの形でLSIに適用することは困難となっています。そこで本研究グループでは、グラフェンの幾何学的構造をナノスケールで制御することで、人工的にバンドギャップを開かせる研究を行っています(図3)[2-4]。これまでに、バンドギャップを開かせたナノ構造グラフェンは、キャリアの有効質量が発生するためグラフェン特有の線形分散が消失する一方で、最適構造を施すことでSiやIII-V族化合物半導体よりも優れたトランジスタ性能を実現することを示してきました[5]。また、グラフェンはアナログ回路への応用も期待されています。アナログ回路は必ずしもバンドギャップを必要としないことから、グラフェンが潜在的に持つ真の超高速性能を発揮できると考えられているからです。本研究グループでは、グラフェンの超高速な信号増幅素子としての可能性を検討しています。

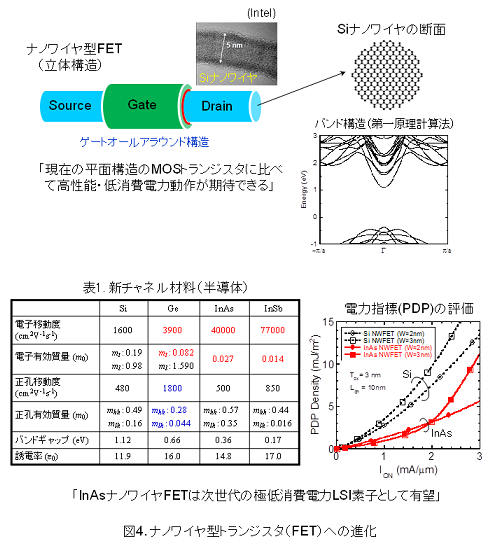

新構造に関しては、従来型の平面構造から脱却し、立体構造のトランジスタを研究しています。FinFETが代表的な立体構造トランジスタで、2011年に米国Intel社から、次世代のCPUに搭載することが発表され大きな注目を集めました。本研究グループでは、FinFETの進化型であるナノワイヤFETに注目しています。ナノワイヤFETは、現在の平面構造のFETに比べて高性能・低消費電力動作が実現できることから、トランジスタ構造の究極形の一つと考えられています(図4)。本研究グループではこれまでに、SiナノワイヤFETやIII-V族ナノワイヤFETの省エネルギー性能の評価を通して、ナノワイヤFETの材料選択の指針を提示してきました[6-9]。

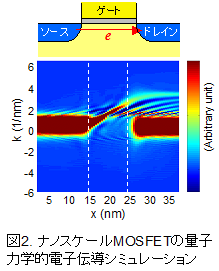

新材料・新構造CMOSデバイスの研究では、量子力学に立脚したナノデバイスシミュレータの開発が鍵となります(図2)[10]。ナノスケールで現われる新しい物理現象を解明しながら、そのエレクトロニクス応用に向けた具体的な指針の構築を目指して研究を進めています。

References

[1] Y. Maegawa, S. Koba, H. Tsuchiya, and M. Ogawa, Applied Physics Express, 4 (2011) 084301.

[2] R. Sako, H. Hosokawa, and H. Tsuchiya, IEEE Electron Device Letters, 32 (2011) 6.

[3] R. Sako, H. Tsuchiya and M. Ogawa, IEEE Trans. on Electron Devices, 58 (2011) 3300.

[4] R. Sako, N. Hasegawa, H. Tsuchiya, and M. Ogawa, Journal of Applied Physics, 113 (2013) 143702.

[5] H. Hosokawa, R. Sako, H. Ando, and H. Tsuchiya, Japanese Journal of Applied Physics, 49 (2010) 110207.

[6] N. Takiguchi, S. Koba, H. Tsuchiya, and M. Ogawa, IEEE Trans. on Electron Devices, 59 (2012) 206.

[7] Y. Yamada, H. Tsuchiya, and M. Ogawa, Journal of Applied Physics, 111 (2012) 063720.

[8] K. Shimoida, Y. Yamada, H. Tsuchiya and M. Ogawa, IEEE Trans. on Electron Devices, 60 (2013) 117.

[9] K. Shimoida, H. Tsuchiya, Y. Kamakura, N. Mori, and M. Ogawa, Applied Physics Express, 6 (2013) 034301.

[10] S. Koba, H. Tsuchiya, and M. Ogawa, Ext. Abst. of International Conference on Simulation of Semiconductor Processes and Devices (SISPAD'11), Osaka, pp. 79-82, 2011.

Go to page top

■新原理・新概念デバイス

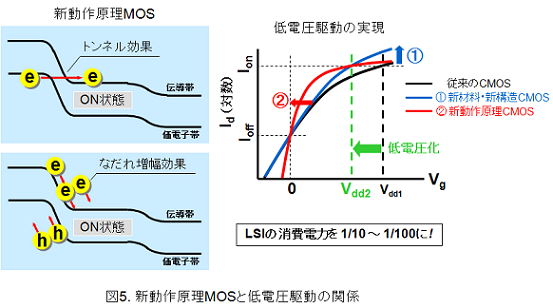

新しい原理や概念を導入した極低消費電力化の試みが始まっています。新しい動作原理は現在までに数多く提案されていて、中でも図5のトンネル効果となだれ増幅効果(インパクトイオン化)が注目を集めています。これらの原理を用いてMOS型トランジスタを動作させると、従来型原理に比べてサブスレッショルド特性を急峻にできるため、より低電圧でスイッチを駆動(オン)させることが可能となり、LSIの消費電力を1/10〜1/100に低減できると考えられています。

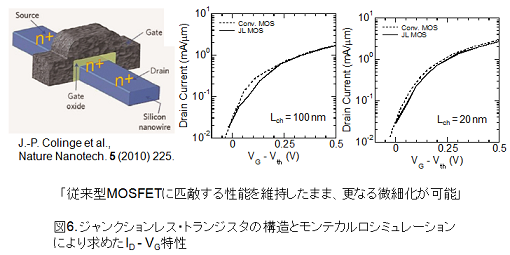

一方、チャネルのドーピング濃度と種類をソース及びドレインと一致させるジャンクションレス・トランジスタ(Junction-Less Transistor:JLT)が最近提案されました(図6)。これは動作原理は従来型と同じですが、これまでのトランジスタ理論では不可欠とされていたpn接合を必要としないため(ジャンクション(接合)レス)、LSI製造を大幅に単純化できると言われています。キャリア輸送の観点からは従来の反転層型トランジスタに比べて、優れた輸送特性を示すことが分かっています。すなわち、JLTのオン状態は蓄積モードで電流が流れるため、キャリアは反転層移動度よりも高いバルク移動度に近い値で流れるようになります。また、ゲート酸化膜界面から離れた場所をキャリアが流れるため、界面ラフネス散乱の影響を軽減することも可能です。界面ラフネス散乱の軽減に関しては、特に、酸化膜界面の品質に課題が残っているIII-Vチャネルトランジスタにおいて力を発揮すると期待できます。本研究グループではこれまでに、モンテカルロシミュレーションを用いてJLTの性能評価を行い、従来型MOSFETに匹敵する性能を維持したまま、更なる微細化が可能であることを示してきました[1-3]。JLTでは正常なオフ動作を実現させるためにFin構造やナノワイヤ構造が必須と考えられることから、ナノワイヤ型JLTの性能を明らかにする研究を進めています。将来的には、III-VチャネルJLTの性能評価にも取り組んで行く予定です。

References

[1] J. Choi, K. Nagai, S. Koba, H. Tsuchiya, and M. Ogawa, Applied Physics Express, 5 (2012) 054301.

[2] K. Nagai, S. Koba, H. Tsuchiya, and M. Ogawa, Ext. Abst. of International Conference on Solid State Devices and Materials

(SSDM'12), PS-3-13, Kyoto, 2012.

[3] K. Nagai, H. Tsuchiya, and M. Ogawa, Japanese Journal of Applied Physics, 52 (2013) 044302.

Go to page top

第27回 「神戸大学公開講座・ひょうご講座」(平成21年6月20日)

講演題目: 暮らしとナノエレクトロニクス (PPT資料)

第9回 「KOBE工学サミット」(平成18年12月1日)

講演題目: シリコンVLSIの微細化とナノMOSトランジスタ