量子力学に立脚したデバイスモデリング

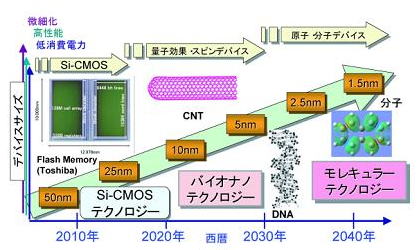

近年,半導体デバイスの微細化の流れが急速に進んでおり,これに伴い,従来用いられてきた半古典論(電子を古典力学的な粒子として捉える)に基づくデバイスモデルの信頼性が揺らぎ始めています.実際,半導体デバイスのサイズはナノスケール(1ミリの1000分の1の更に1000分の1)へと向かって微細化が進められており,従来の単純な半古典輸送モデルでは現在開発が進められているデバイスにおける特性の予測が困難であり,量子輸送理論に立脚した量子力学的デバイスシミュレーションが重要であることが認識され始めています。

Nano MOS シミュレーション

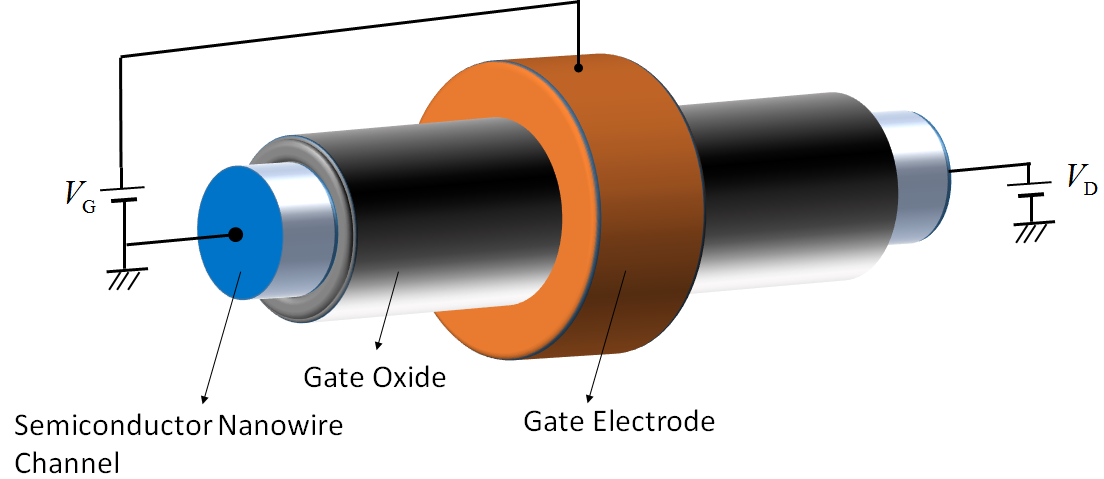

シリコン電界効果トランジスタ(MOSFET)のチャネル材料やチャネル構造を改良することで性能向上を図ろうとする試みが近年脚光を浴びています.そのチャネル構造の革新には主に二つの方向性があります.一つは,チャネルの速度・移動度を向上させるために新チャネル材料を用いる技術であり,もう一つは,短チャネル効果を抑制するために超薄膜SOI化およびマルチゲート化する技術です.これらの新技術が使われる技術世代を考えると,チャネルの断面構造やゲート絶縁膜等はナノスケールのサイズになるため,その電子状態や電子輸送を深く理解するには,量子輸送理論に立脚した量子力学的デバイスシミュレーションが不可欠となってきます.当研究室では,これまで「非平衡グリーン関数法」や「量子補正を導入したモンテカルロ法」などの先駆的なデバイス設計ツールを提案・開発し,国内外から高い評価を頂いています.将来はさらに,原子レベルでのデバイス解析が不可欠になるとの認識から,強束縛近似法や第一原理計算法と融合させた量子力学的デバイスシミュレーションの開発を進めています.

ナノマテリアルデザイン

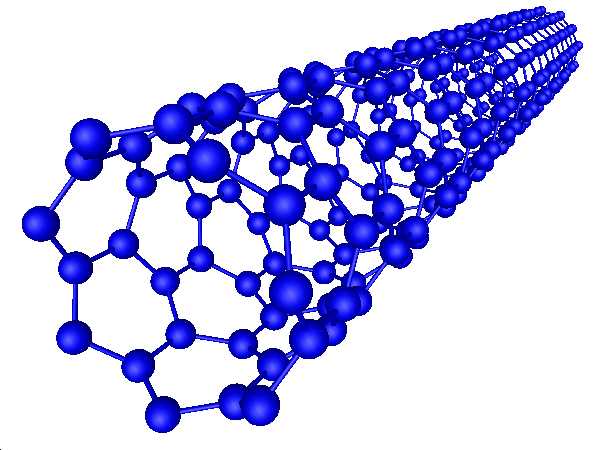

ナノメートルサイズは原子数個の大きさに相当します.このため,ナノメートルサイズの材料及びデバイス設計には,従来のマクロスコピックな現象論に代わり,個々の原子の挙動を忠実に再現する第一原理計算法が用いられます.第一原理計算法とは,固体の電子状態や物性を研究することを目的として,シュレディンガー方程式を解いて,物質を構成する多数の原子核がつくるポテンシャル中の電子の挙動をできるだけ正確に取り扱う手法です.当研究室では,第一原理計算法を駆使して,大規模集積回路(VLSI)の基本素子であるMOSFETの極限性能を探索する研究や,新型構造デバイスとして注目されているシリコンナノワイヤのデバイス設計指針,さらにはカーボンナノチューブの電子状態の解明を目指した研究を進めています。

新概念エレクトロニクス

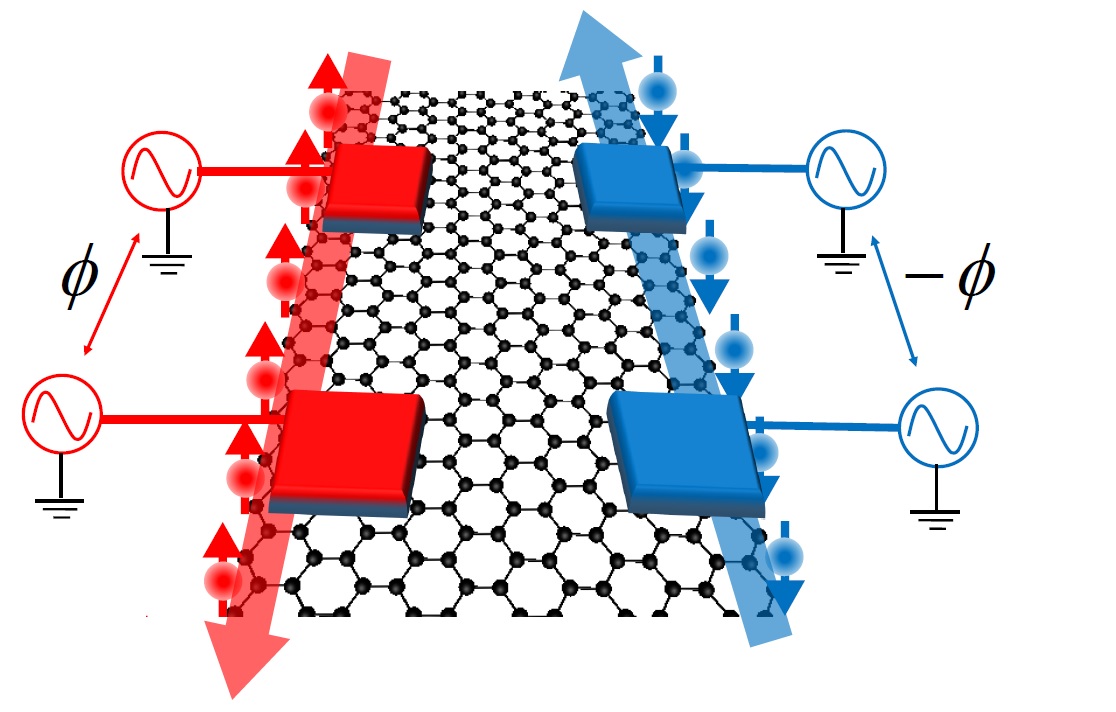

「トンネル電流で制限されるMOSFETのゲート長は2nm,実用的にはゲート長10~5nmがMOSFETの微細化限界ではないか」(東京工業大学教授の岩井洋氏)と考えられるようになってきています.その先にあるポストCMOSデバイスとして期待されている情報処理デバイスの一つが「分子デバイス」です.分子デバイスは,そのサイズがナノスケールから原子スケールであることに加え,消費電力が極めて小さいこと等から,集積化デバイスとして非常に魅力的な潜在能力を有しています.当研究室では,様々な有機分子や,カーボンナノチューブ,グラフェンなどの炭素系ナノ構造素子の特性に関する研究を進めています. 又,従来のエレクトロニクスでは電子の持つ「電荷」という属性を利用して情報の伝達を行ってきていましたが,近年,電子の持つもうひとつの属性である「スピン自由度」を積極的に用いて電子デバイス制御を行おうとする試み「スピンエレクトロニクス」が近年注目を集めています.この「スピンエレクトロニクス」においても消費電力を軽減出来るというメリットがあります.当研究室では,このスピンエレクトロニクス素子の可能性を更に明らかにするべく,研究を進めています.